**BACHELOR THESIS**

Tom Hert

# Porting RIOT OS to the RP2350: An Exploration of a Heterogeneous Architecture and Programmable I/O

---

Faculty of Computer Science and Digital Society

Tom Hert

# Porting RIOT OS to the RP2350: An Exploration of a Heterogeneous Architecture and Programmable I/O

Bachelor thesis submitted for examination in Bachelor's degree

in the study course *Bachelor of Science Informatik Technischer Systeme*

at the Faculty of Computer Science and Digital Society

at University of Applied Science Hamburg

---

Supervising examiner: **Prof. Dr. Thomas C. Schmidt**

Second examiner: **Prof. Dr. Franz Korf**

---

Submitted on: January 15, 2026

**Tom Hert**

**Title of thesis**

Porting RIOT OS to the RP2350: An Exploration of a Heterogeneous Architecture and Programmable I/O

**Keywords**

RISC-V, RIOT OS, ARM, Embedded Systems, Operating System

**Abstract**

A recent development in the field of embedded systems is the emergence of heterogeneous architectures, which combine multiple types of processors on a single chip. The Raspberry Pi RP2350 is one such architecture, combining two ARM Cortex M33 and two Hazard3 RISC-V cores, along with a Programmable Input/Output (PIO) subsystem. Currently, RIOT OS, a popular operating system for embedded devices, does not support such architectures.

This thesis, explores the challenges and opportunities involved in porting RIOT OS to the RP2350. It focuses on understanding the architecture, implementing the necessary low-level support, and evaluating the advantages of such a system, including multicore processing in embedded applications.

**Tom Hert**

**Thema der Arbeit**

Portierung von RIOT OS auf den RP2350: Eine Untersuchung einer heterogenen Architektur und programmierbarer I/O

**Stichworte**

RISC-V, RIOT OS, ARM, Eingebettete Systeme, Betriebssystem

**Kurzzusammenfassung**

Eine aktuelle Entwicklung in der Welt der eingebetteten Systeme ist das Vorhandensein heterogener Architekturen, die mehrere Prozessortypen auf einem einzigen Chip

kombinieren. Der Raspberry Pi RP2350 ist eine solche Architektur, die zwei ARM Cortex M33- und zwei Hazard3 RISC-V-Kerne sowie ein PIO Subsystem kombiniert. Derzeit werden solche Architekturen in RIOT OS, einem beliebten Betriebssystem für eingebettete Geräte, nicht unterstützt.

Diese Arbeit untersucht die Herausforderungen und Chancen der Portierung von RIOT OS auf den RP2350, wobei der Schwerpunkt auf dem Verständnis der Architektur, der Implementierung der erforderlichen Low-Level-Unterstützung und der Bewertung der Vorteile eines solchen Systems liegt. Dabei ist auch ein Fokus auf die Möglichkeiten der Multi-Core Verarbeitung in eingebetteten Anwendungen bietet.

# Contents

|                                                                                         |             |

|-----------------------------------------------------------------------------------------|-------------|

| <b>List of Figures</b>                                                                  | <b>viii</b> |

| <b>List of Tables</b>                                                                   | <b>x</b>    |

| <b>Listings</b>                                                                         | <b>xi</b>   |

| <b>Abbreviations</b>                                                                    | <b>xiii</b> |

| <b>1 Introduction</b>                                                                   | <b>1</b>    |

| 1.1 Motivation .....                                                                    | 1           |

| 1.2 Objective .....                                                                     | 2           |

| 1.3 Outline .....                                                                       | 2           |

| <b>2 Background</b>                                                                     | <b>4</b>    |

| 2.1 RISC-V .....                                                                        | 4           |

| 2.2 ARM-M .....                                                                         | 4           |

| 2.3 RIOT OS .....                                                                       | 5           |

| 2.3.1 RIOT OS Support for New Microcontroller (Unit)s (MCUs) .....                      | 5           |

| 2.3.2 RIOT Principles .....                                                             | 6           |

| 2.4 RP2350 .....                                                                        | 7           |

| 2.4.1 RP2350 Overview .....                                                             | 7           |

| 2.4.2 Hazard3 .....                                                                     | 8           |

| 2.4.3 Cortex-M33 .....                                                                  | 8           |

| 2.4.4 Programmable Input/Output (PIO) .....                                             | 10          |

| 2.4.5 Inter-Processor Communication .....                                               | 11          |

| <b>3 Related Work</b>                                                                   | <b>14</b>   |

| 3.1 Inferno OS on ARMv7-M .....                                                         | 14          |

| 3.2 Security through Transparency: Tales from the RP2350 Hacking Challenge ..           | 15          |

| 3.3 Evaluation of RISC-V Physical Memory Protection in Constrained IoT<br>Devices ..... | 15          |

|                                                             |           |

|-------------------------------------------------------------|-----------|

| 3.4 ArielOS . . . . .                                       | 16        |

| 3.5 Pico SDK . . . . .                                      | 18        |

| 3.5.1 Abstraction . . . . .                                 | 18        |

| 3.6 ZephyrOS . . . . .                                      | 19        |

| <b>4 Analysis and Design</b>                                | <b>20</b> |

| 4.1 Bootup Sequence . . . . .                               | 20        |

| 4.1.1 Bootrom . . . . .                                     | 20        |

| 4.1.2 Flashing . . . . .                                    | 20        |

| 4.1.3 Image and Partition Definition (Picobin) . . . . .    | 22        |

| 4.2 Interrupt Controller . . . . .                          | 23        |

| 4.2.1 Nested Vectored Interrupt Controller (NVIC) . . . . . | 24        |

| 4.2.2 XH3IRQ Controller . . . . .                           | 24        |

| 4.2.3 Design Considerations . . . . .                       | 26        |

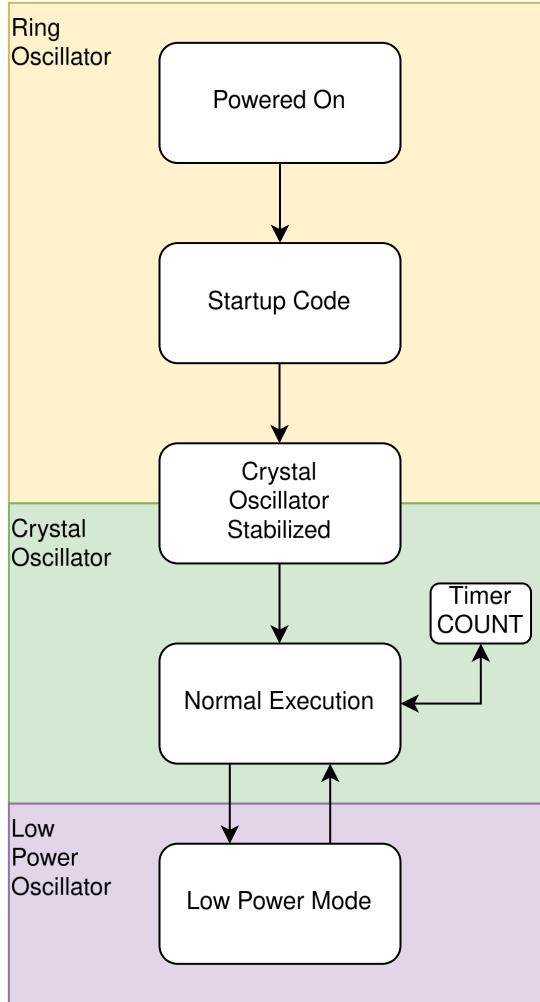

| 4.3 Clocks . . . . .                                        | 29        |

| 4.3.1 Ring Oscillator (ROSC) . . . . .                      | 29        |

| 4.3.2 Crystal Oscillator (XOSC) . . . . .                   | 29        |

| 4.3.3 Low Power Oscillator (LPOSC) . . . . .                | 30        |

| 4.3.4 Design Considerations . . . . .                       | 30        |

| 4.4 Multi-Core Support . . . . .                            | 31        |

| 4.4.1 Background . . . . .                                  | 31        |

| 4.4.2 Design Proposal . . . . .                             | 33        |

| 4.5 Programmable Input/Output (PIO) . . . . .               | 33        |

| <b>5 Implementation</b>                                     | <b>35</b> |

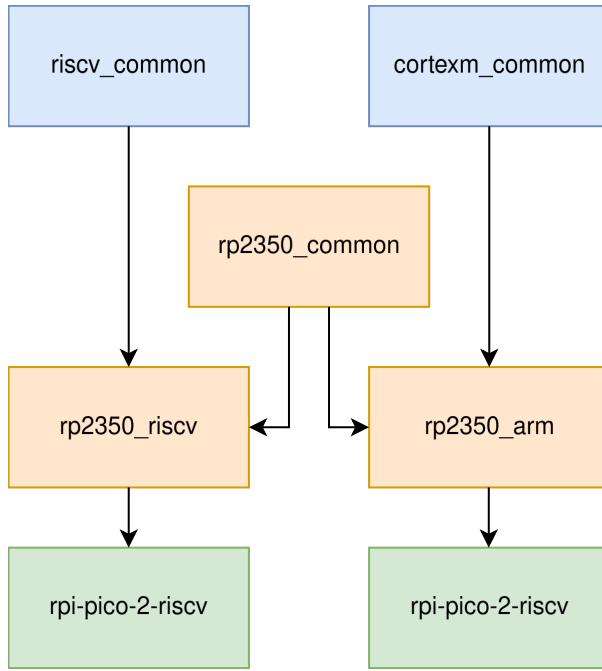

| 5.1 Module Setup and Abstraction . . . . .                  | 35        |

| 5.1.1 Module Structure . . . . .                            | 35        |

| 5.1.2 Build System Architecture Abstraction . . . . .       | 36        |

| 5.1.3 Build System . . . . .                                | 37        |

| 5.1.4 Picobin Integration . . . . .                         | 39        |

| 5.2 Interrupt Handling . . . . .                            | 41        |

| 5.2.1 RISC-V Interrupt Handling . . . . .                   | 41        |

| 5.2.2 ARM Interrupt Handling . . . . .                      | 43        |

| 5.3 Multicore Implementation . . . . .                      | 43        |

| 5.4 Implementation of Clocks . . . . .                      | 46        |

| 5.5 Programmable Input/Output (PIO) Support . . . . .       | 46        |

|                                                        |           |

|--------------------------------------------------------|-----------|

| 5.5.1 Abstracting PIO Instruction Generation . . . . . | 47        |

| 5.5.2 PIO Usage Example . . . . .                      | 48        |

| <b>6 Evaluation</b>                                    | <b>50</b> |

| 6.1 Multicore Support . . . . .                        | 50        |

| 6.1.1 Methodology . . . . .                            | 50        |

| 6.1.2 Results . . . . .                                | 51        |

| 6.1.3 Discussion . . . . .                             | 52        |

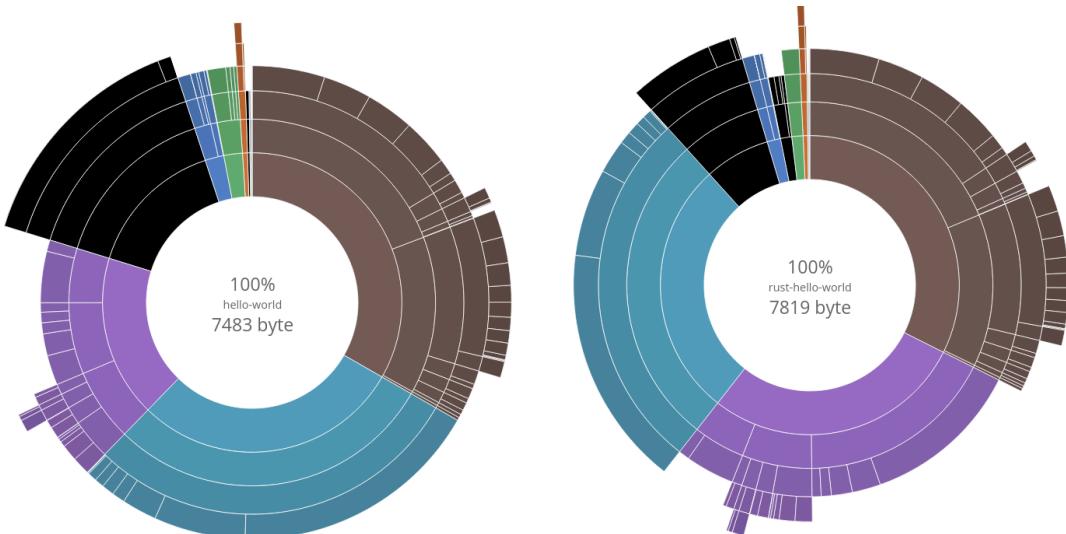

| 6.2 Code Size Comparison . . . . .                     | 53        |

| 6.2.1 Methodology . . . . .                            | 53        |

| 6.2.2 Results . . . . .                                | 53        |

| 6.2.3 Analysis . . . . .                               | 55        |

| 6.2.4 Comparison with Pico SDK . . . . .               | 57        |

| 6.3 Benefits of RIOT on RP2350 . . . . .               | 58        |

| 6.3.1 Unit Tests / Integration Tests . . . . .         | 58        |

| 6.3.2 Rust Integration . . . . .                       | 59        |

| 6.3.3 Accessing Third Party Libraries . . . . .        | 60        |

| 6.3.4 PMP Support . . . . .                            | 60        |

| <b>7 Conclusion</b>                                    | <b>62</b> |

| <b>8 Outlook</b>                                       | <b>64</b> |

| 8.1 TrustZone-M and Security Features . . . . .        | 64        |

| 8.2 Heterogeneous Core Utilization . . . . .           | 64        |

| 8.3 USB Support . . . . .                              | 64        |

| 8.4 Advanced Multi-Core Features . . . . .             | 65        |

| <b>Glossary</b>                                        | <b>66</b> |

| <b>Bibliography</b>                                    | <b>68</b> |

| <b>Declaration of Independent Processing</b>           | <b>71</b> |

# List of Figures

|          |                                                                                                                                                                                                                                                                                                      |    |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

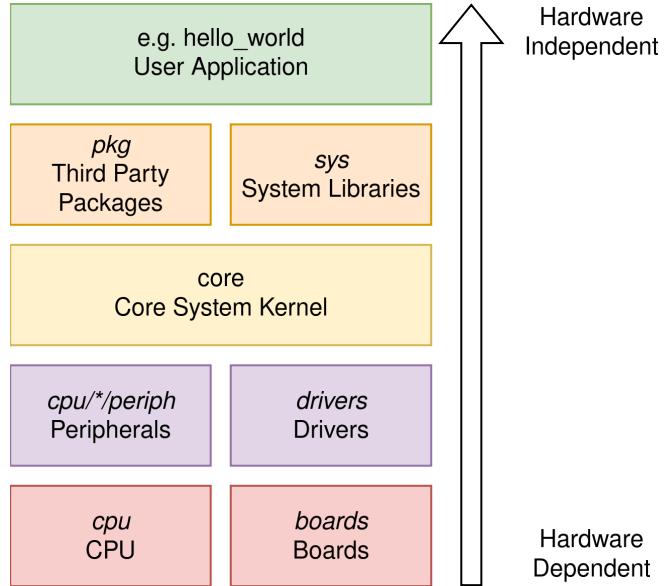

| Figure 1 | RIOT OS modular architecture showcasing the kernel, drivers, and applications. Going from highly hardware-dependent modules to hardware-agnostic ones. . . . .                                                                                                                                       | 6  |

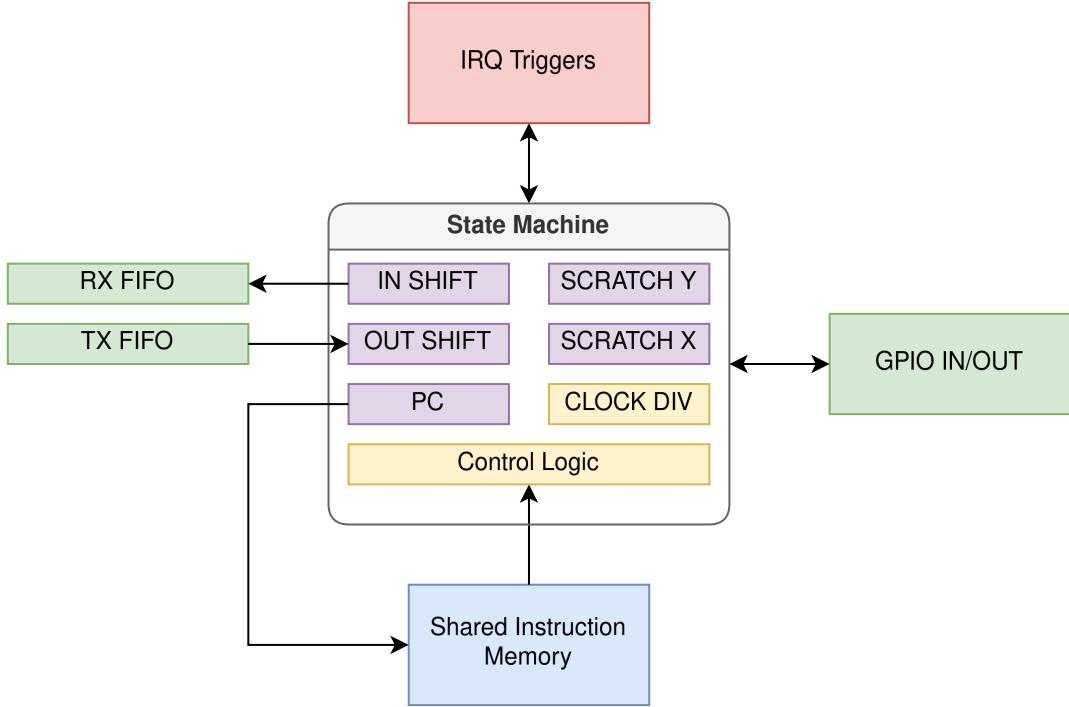

| Figure 2 | Overview of a PIO state machine. Showcasing the shared instruction memory, access to the FIFO buffer, and interrupts. . . . .                                                                                                                                                                        | 10 |

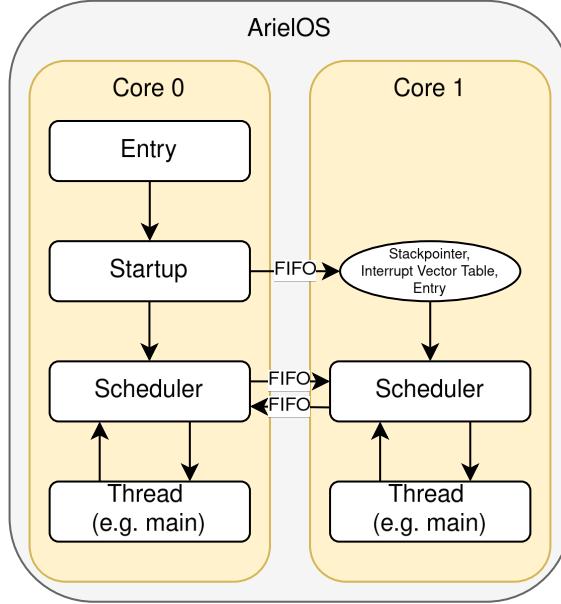

| Figure 3 | ArielOS Scheduler Architecture. After startup, Core 0 initializes the system and starts Core 1 via the FIFO (See Section 2.4.5.4). Then, both cores run the same scheduler, triggered through FIFO messages from either core to handle task scheduling. . . . .                                      | 17 |

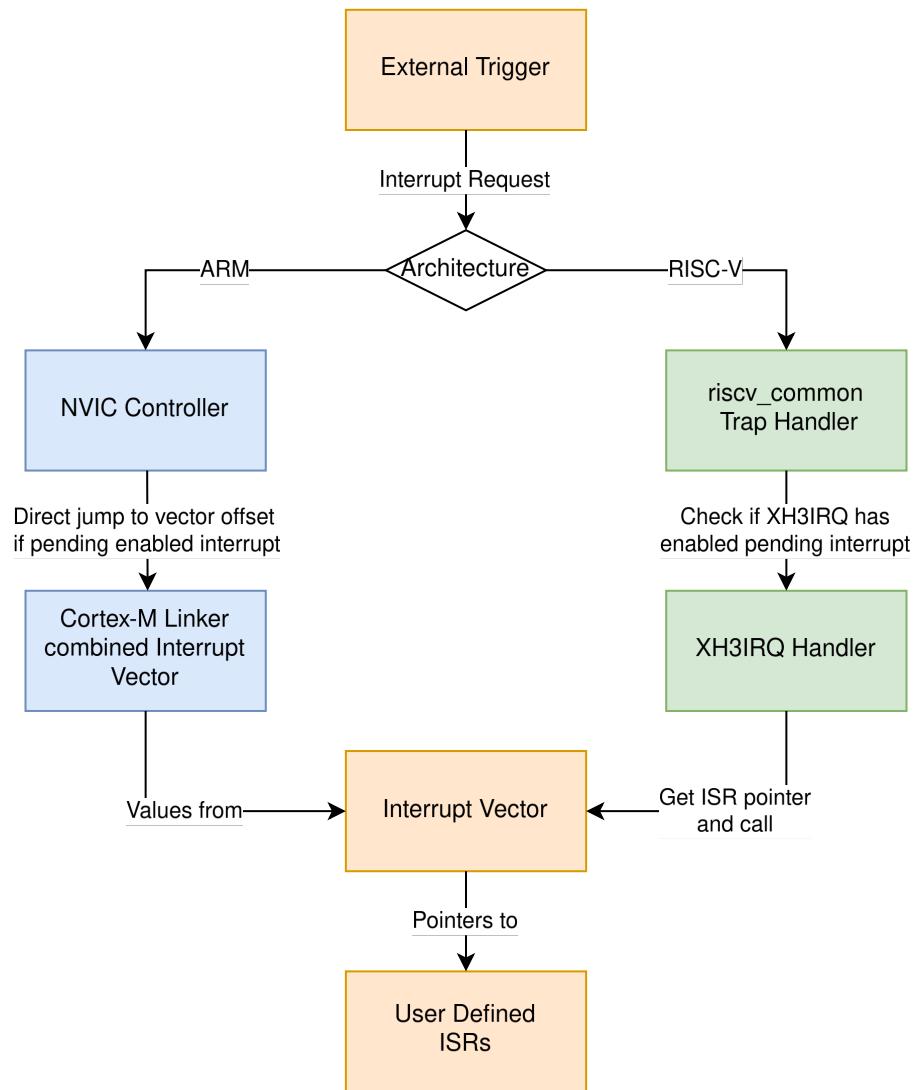

| Figure 4 | Diagram showing the design proposal for the route a hardware interrupt takes through the abstraction layers. Starting from the external trigger to the final user-defined Interrupt Service Routine (ISR) handler. Orange boxes are shared/common, blue boxes are ARM, green boxes are RISC-V. . . . | 27 |

| Figure 5 | Proposed clock startup sequence for RP2350 port in RIOT OS. First, while running via ROSC, the XOSC is enabled. After a delay to allow it to stabilize, the system clock is switched to the XOSC for stable operation. .                                                                             | 30 |

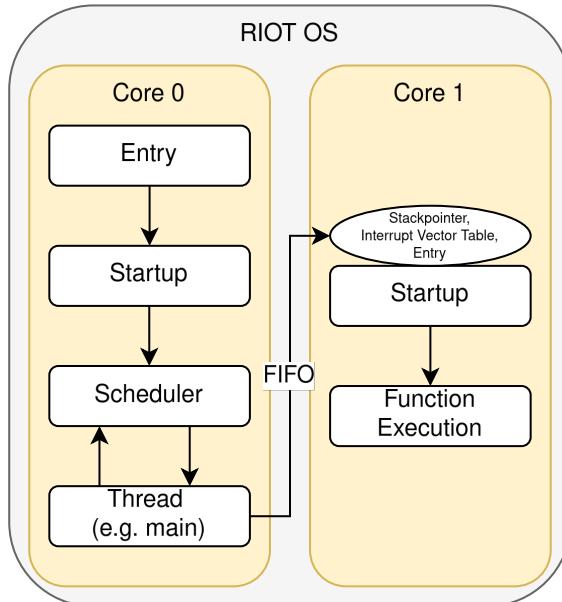

| Figure 6 | Proposed “Worker Core” multi-core model for RIOT OS. The main core (Core 0) offloads specific tasks to the secondary core (Core 1) which runs them independently without any scheduler intervention. . . . .                                                                                         | 33 |

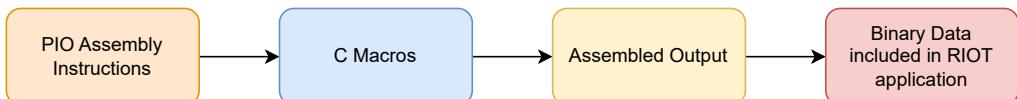

| Figure 7 | Proposed design for integrating <code>pioasm</code> into the RIOT build system. The <code>pioasm</code> tool is built from the Pico SDK and then used to assemble PIO assembly files into raw binary data that can be included in the RIOT build process. . . . .                                    | 33 |

| Figure 8 | RIOT OS RP2350 module folder structure. Blue denotes architecture-specific modules. Orange denotes CPU module definitions. Green denotes MCU Development Board (board) module definitions. . . . .                                                                                                   | 36 |

## *List of Figures*

# List of Tables

|          |                                                                                                                                                                             |    |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 1  | RISC-V extensions supported by Hazard3                                                                                                                                      | 8  |

| Table 2  | PIO assembly instructions                                                                                                                                                   | 10 |

| Table 3  | Picobin block structure for RP2350 image definition                                                                                                                         | 22 |

| Table 4  | XH3IRQ custom CSRs for interrupt management [1, Chapter 4.1]                                                                                                                | 25 |

| Table 5  | XH3IRQ CSRs register fields for Interrupt Pending Array ( <code>meipa</code> ), Interrupt Enable Array ( <code>meiea</code> ), Force Interrupt Array ( <code>meifa</code> ) | 25 |

| Table 6  | XH3IRQ CSRs register fields for the Interrupt Priority Array ( <code>meipra</code> )                                                                                        | 25 |

| Table 7  | Values sent to the secondary core via inter-processor FIFO during boot.                                                                                                     | 43 |

| Table 8  | ARM memory section breakdown by component                                                                                                                                   | 54 |

| Table 9  | ARM cpu text section breakdown by module (left) and rp2350_common text section breakdown (right)                                                                            | 55 |

| Table 10 | RISC-V memory section breakdown by component                                                                                                                                | 55 |

| Table 11 | RISC-V cpu text section breakdown by module (left) and rp2350_common text section breakdown (right)                                                                         | 55 |

| Table 12 | Memory comparison between Pico SDK and RIOT OS for dual-core GPIO application on the ARM Cortex-M33 cores                                                                   | 57 |

# Listings

|            |                                                                                                                                                                                                                                                                                                                                 |    |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Listing 1  | Example of architecture-specific IRQ enabling through abstraction in <code>rp2350_common</code> . . . . .                                                                                                                                                                                                                       | 36 |

| Listing 2  | Example of the ARM <code>cpu_init</code> function within the <code>rp2350_common</code> module. . . . .                                                                                                                                                                                                                         | 37 |

| Listing 3  | The shared <code>rp2350_init</code> function within the <code>rp2350_common</code> module. Initializes clocks, GPIO, and peripherals. . . . .                                                                                                                                                                                   | 37 |

| Listing 4  | Example of the RISC-V CPU module <code>Makefile</code> including the shared <code>rp2350_common</code> and <code>riscv_common</code> feature files. . . . .                                                                                                                                                                     | 38 |

| Listing 5  | Excerpt of modified linker script from <code>cortexm_common</code> module to include picobin block . . . . .                                                                                                                                                                                                                    | 39 |

| Listing 6  | Excerpt of modified linker script from <code>riscv_common</code> module to include picobin block . . . . .                                                                                                                                                                                                                      | 39 |

| Listing 7  | Assembly code for the picobin block used in RP2350 builds, based on the definitions in Section 4.1.3. . . . .                                                                                                                                                                                                                   | 41 |

| Listing 8  | Checking the Machine Interrupt Pending CSR for pending interrupts in <code>trap_handler</code> . . . . .                                                                                                                                                                                                                        | 42 |

| Listing 9  | Fetching the highest priority pending interrupt from the <code>MEINEXT</code> CSR and calling the appropriate ISR from the shared vector table in <code>xh3irq_handler</code> . . . . .                                                                                                                                         | 42 |

| Listing 10 | Sequence to send the necessary boot values to the secondary core via inter-processor FIFO. First, draining the read FIFO if the value to send is <code>0</code> , then sending the value and waiting for an echoed response before proceeding to the next value. On each incorrect response, the sequence is restarted. . . . . | 45 |

| Listing 11 | Example of C macros to generate PIO instructions, specifically the <code>JMP</code> instruction with conditional and unconditional variants. . . . .                                                                                                                                                                            | 48 |

| Listing 12 | Example of using the PIO abstraction layer to create a simple square wave generator on GPIO0 using PIO0. The program sets the pin high and low in                                                                                                                                                                               |    |

|                                                                                                                                       |    |

|---------------------------------------------------------------------------------------------------------------------------------------|----|

| a loop, creating a square wave output. The GPIO pin is initialized for PIO usage using the modified GPIO driver. . . . .              | 49 |

| Listing 13 Single-core GPIO toggling both pins sequentially (left) and dual-core GPIO toggling both pins in parallel (right). . . . . | 51 |

# Abbreviations

*CLIC* – Core Local Interrupt Controller

*ISR* – Input Shift Register

*LPOSC* – Low Power Oscillator

*NVIC* – Nested Vectored Interrupt Controller

*OSR* – Output Shift Register

*PLIC* – Platform Level Interrupt Controller

*ROSC* – Ring Oscillator

*XOSC* – Crystal Oscillator

*board* – MCU Development Board

*IoT* – Internet of Things

*IRQ* – Interrupt Request

*ISA* – Instruction Set Architecture

*ISR* – Interrupt Service Routine

*LR/SC* – Load-Reserved/Store-Conditional

*MCU* – Microcontroller (Unit)

*OS* – Operating System

*OTP* – One-Time Programmable

*PIO* – Programmable Input/Output

*PMP* – Physical Memory Protection

*PSM* – Power State Machine

*RISC* – Reduced Instruction Set Computing

# 1 Introduction

## 1.1 Motivation

In recent years, ARM has dominated the embedded systems industry, offering relatively fast Microcontroller Units (MCUs) such as the Cortex-M series, at comparatively low prices.

The emergence of RISC-V has challenged that dominance by offering an open alternative, which allows anyone to design and manufacture their own RISC-V-based MCUs without paying licensing fees to ARM. This has led to a surge of innovation in the field of MCUs, with many new designs and architectures being developed [2].

To ease developers into the usage of RISC-V based devices, Raspberry Pi released the RP2350 MCU. This MCU combines the legacy and wide adoption of the ARM Cortex-M33 with the flexibility of the new RISC-V architecture using a Hazard3 open-source core [3].

This heterogeneous dual-core design is unified through an MCU architecture that emphasizes a shared environment, including common board peripherals, memory, and programmable I/O (PIO) blocks. This makes the RP2350 a unique platform for experimenting with heterogeneous architectures in the embedded systems world.

RIOT OS is an open-source operating system designed for low-end IoT devices. It is known for its modularity, efficiency, and broad hardware support. It is designed to be hardware-agnostic and portable across different architectures and boards [4]. Still, RIOT OS currently does not support MCUs with heterogeneous architectures such as the RP2350.

## 1.2 Objective

This thesis explores the process of porting RIOT OS to the RP2350 MCU, leveraging its unique dual-core architecture to enhance the capabilities of RIOT. The goal is to implement a functional port that allows RIOT OS to run seamlessly on the RP2350, taking advantage of its heterogeneous architecture while maintaining the modularity and efficiency that RIOT OS prides itself on [4].

The main objective of this work is to create a unified abstraction layer for both architectures that allows seamless switching between RISC-V and ARM with minimal code redundancy. This entails exploring methods of integrating with the existing codebase of RIOT while also conforming to the unique peculiarities of the RP2350, such as the custom interrupt controller which the Hazard3 RISC-V processor includes.

In this thesis, we will also take a first glance at multicore processing within RIOT OS, exploring how a heterogeneous dual-core architecture can be utilized in an embedded operating system context. The objective of this thesis is to have a functional RIOT OS port for the RP2350 that can serve as a foundation for future work and exploration of heterogeneous architectures in embedded systems.

## 1.3 Outline

Section 2 provides the relevant background information on the RP2350 architecture, and relevant concepts, such as heterogeneous architectures and programmable I/O, as well as its multicore processing. It also gives an introduction to the RIOT operating system and design principles.

A review of related work in Section 3 follows next. In it, both related academic work and existing implementations of the RP2350 on other operating systems and libraries are discussed, with differences and similarities in our approach and goals being explained.

In Section 4 the thesis analyzes the RP2350 in more detail to explore the requirements and design considerations that are relevant for the porting process. We examine the boot process, multicore startup sequence, and interrupt system in detail. We also explore RP2350-specific details such as the picobin image format and Hazard3 custom extensions.

After diving into these details, we then describe the implementation of the port in Section 5. Detailing the steps taken to implement low-level support for the RP2350 architecture, including clock configuration. Describing the approach that was taken to

implement multicore support and a unified abstraction for both architectures. We also discuss our approach to integrating the RP2350 interrupt controller with the existing RIOT interrupt handling system.

In Section 6, we evaluate the functionality and performance of the RIOT OS port on the RP2350. Showcasing the benefits that a second core can bring to an embedded operating system. We also compare differences in performance and size between the ARM and RISC-V cores when running RIOT-OS.

Finally, Section 7 wraps up the thesis by summarizing the key findings and contributions of this work. We reflect on the challenges faced during the porting process and how they were addressed. We also discuss the implications of our work for the future of RIOT OS and heterogeneous architectures in embedded systems. Followed by a discussion of potential future directions and improvements that can be made based on the work of this thesis in Section 8.

## 2 Background

### 2.1 RISC-V

RISC-V is an open-standard Instruction Set Architecture (ISA) based on established principles of Reduced Instruction Set Computing (RISC) [5].

The RISC design philosophy aims to simplify the processor design by using a small set of simple and general instructions. This allows for easier implementation, lower power consumption, and higher performance by moving complexity from the hardware to the software, such as compilers and assemblers that can optimize instruction usage.

RISC-V expands on this concept by being open and extensible, allowing anyone to design, manufacture, and sell RISC-V processors without any licensing agreements. This has led to a wide range of adoptions, from small MCUs to high-performance processors, including the Hazard3 open-source core used by the RP2350.

RISC-V is still a relatively new architecture compared to architectures such as ARM and x86. However, it has gained significant traction in recent years, experiencing a 276.8% growth from 2022 to 2023 with market analysts such as the SHD Group forecasting continuing rapid growth over the next decades [6].

### 2.2 ARM-M

The ARM-M family comprises RISC processors designed by ARM Holdings plc. Unlike RISC-V, ARM is a proprietary architecture, requiring companies to license the technology from ARM Holdings plc when used in their products<sup>1</sup>.

---

<sup>1</sup>ARM licensing information can be found here (Accessed 30.10.2025): <https://www.arm.com/products/licensing>

The ARM-M family is designed for low-power, cost-efficient processors, making it ideal for embedded systems and IoT devices. It features a simplified instruction set, a limited number of registers, and other optimizations intended for embedded systems.

The ARM-M architecture also includes various security features, such as TrustZone technology, which allows for the creation of secure and non-secure execution environments, as has been explored for RIOT OS in “Integration and Evaluation of a Secure Firmware for Arm Cortex-M Devices in RIOT OS”[7].

While RISC-V is gaining traction in the embedded systems industry [6], ARM-M remains a dominant architecture for low-power embedded systems due to its maturity, extensive ecosystem, and wide range of available tools and libraries, including the Cortex-M series of processors, such as the RP2350 Cortex-M33 core.

## 2.3 RIOT OS

RIOT OS is an open-source Operating System (OS) for low-end embedded devices in the Internet of Things (IoT). It is vendor-neutral and lightweight on as little as 3.2 kB of ROM and 2.8 kB of RAM under minimal configurations [4].

The focus of RIOT on modularity and modifiability facilitates the easy integration of new features, including new MCUs and boards. Accompanied by a comprehensive set of tutorials and documentation to help new users get started with the OS<sup>2</sup>.

RIOT also offers a vast number of packages that can be utilized by newly ported boards after the initial setup. Currently, RIOT does not support heterogeneous architectures or multicore systems.

RIOT does, however, support both ARM and RISC-V architectures, including a comprehensive abstraction for architecture specific common code, which makes it a good candidate for the RP2350.

### 2.3.1 RIOT OS Support for New MCUs

RIOT OS adopts a modular approach to peripheral and module support. Each peripheral or module is implemented as a separate driver that can be included or excluded depending on the target board or MCU [4, Chapter 6].

---

<sup>2</sup>RIOT OS documentation can be found here (Accessed 30.10.2025): <https://guide.riot-os.org/>

The minimal support level RIOT OS requires of any added MCU is a bootable system capable of running a basic application, preferably including threading, though under special circumstances, a single-threaded system is also acceptable [4, Chapter 5].

From there, additional peripherals and most essential functionality can be added incrementally, such as interrupts, timers, GPIO, and UART.

### 2.3.2 RIOT Principles

Figure 1: RIOT OS modular architecture showcasing the kernel, drivers, and applications.

Going from highly hardware-dependent modules to hardware-agnostic ones.

RIOT separates hardware-dependent code from hardware-agnostic code through a layered architecture where each layer only interacts with the layer directly above or below it, rarely crossing layers as seen in Figure 1.

In essence, hardware-dependent code is limited to the MCU `cpu` drivers and `boards` board. The MCU driver, depending on the MCU and board, provides access to peripherals `periph` such as GPIO, timers, UART, SPI, and I<sup>2</sup>C. The board file then maps these peripherals to physical pins and configures any board-specific settings, such as UART baud rate or LED active high/low.

These components use a common peripheral API `drivers / periph` defined by RIOT OS. This API enables hardware-agnostic code, such as network stacks, file systems, and

applications, to use these peripherals without knowledge of the underlying hardware [4, Chapter 6c].

Another useful side effect of this modularity is that swapping out hardware becomes easier. Provided the new hardware has a RIOT OS MCU driver and a board file, the remainder of the system usually remains unchanged.

RIOT also offers third-party packages through the `pkg` directory. These packages can be added to a RIOT OS project through a simple `USEPKG` directive in the `Makefile`, enabling the integration of new functionality without the need to modify the core RIOT OS codebase. Examples include libraries, such as `lvgl` for graphical user interfaces, `micropython` for Python scripting support, or `tinyusb` for USB support<sup>3</sup>.

First-party packages are also modular and can be included from the `sys` directory. This includes essential functionality such as networking, file system, and cryptography.

The `core` directory contains the RIOT OS kernel and essential services such as the scheduler, memory management, and inter-process communication. This layer is hardware-agnostic and can run on every supported MCU<sup>4</sup>.

RIOT ensures that all the aforementioned layers are well tested through a comprehensive suite of unit and integration tests. This testing helps to maintain the stability and reliability of the system as new features and MCU support are added, and existing components are modified<sup>5</sup>.

## 2.4 RP2350

### 2.4.1 RP2350 Overview

The RP2350 is a low-cost MCU developed by Raspberry Pi. The Raspberry Pi Pico 2 serves as the reference board for the RP2350. Throughout this thesis, the terms *RP2350* and *Raspberry Pi Pico 2* are used interchangeably.

The RP2350 features both a dual-core ARM Cortex-M33 and a dual-core Hazard3 RISC-V processor, which can be switched between while retaining full access to peripherals and memory. Both processors run at 150MHz on the Pico 2 board [3, Chapter 1]. The

---

<sup>3</sup>A comprehensive list of available packages can be found here (Accessed 30.10.2025): <https://github.com/RIOT-OS/RIOT/tree/master/pkg>

<sup>4</sup>More information about the RIOT OS structure can be found here (Accessed 30.10.2025): <https://guide.riot-os.org/general/structure/>

<sup>5</sup>CI can be accessed here (Accessed 29.10.2025): <https://ci.riot-os.org/details/branch/master>

Pico 2 board includes 520 kB of SRAM, 4 MB of onboard QSPI flash, two UARTs, two SPI controllers, two I2C controllers, 24 PWM channels, 26 GPIO pins, and three PIO subsystem blocks, each supporting four state machines [8].

The RP2350 is the first heterogeneous architecture developed by Raspberry Pi [9]. It succeeds the RP2040, which includes dual ARM Cortex-M0+ cores, 264kB of SRAM, and the first version of PIO [10]. RIOT OS already includes support for the RP2040, however, the RP2350 drastically changes the architecture by introducing RISC-V cores and a more advanced Cortex-M33 core, thus requiring a new port.

The RP2350 is designed for low-power applications and is suitable for use in a wide range of embedded systems, including IoT devices, wearables, and home automation systems. At the time of writing, three public revisions of the RP2350 exist: RP2350 A2, RP2350 A3, and RP2350 A4, released in July 2025. These mostly contain bug fixes and security improvements [3, Appendix C]. This thesis is based on revision RP2350 A3 of the RP2350, as revision A4 was released after the initial research phase.

## 2.4.2 Hazard3

Hazard3 is a three-stage pipelined RISC-V processor used by Raspberry Pi in the RP2350 MCU. It was designed by Luke Wren and is open-source [16]. The Hazard3 includes various extensions that introduce new CSRs and instructions, as listed in Table 1.

Although the Hazard3 is designed with modularity in mind, this thesis assumes that all of the above extensions are present, given that they are all implemented by the RP2350 [3, Chapter 3.8].

### 2.4.2.1 Physical Memory Protection (PMP)

Physical Memory Protection (PMP) is a security feature of RISC-V that allows the definition of memory regions with specific access permissions [14, Chapter 3.7].

Although the Hazard3 supports 16 PMP regions [1, Chapter 3.3], the RP2350 implementation is configured for only eight PMP regions at 32-byte granularity, followed by three hard-wired regions [3, Chapter 10.4].

The RIOT implementation of PMP follows the ISA specification, where only 16 or 64 regions are supported [17, Chapter 2.2.4].

## 2.4.3 Cortex-M33

The Cortex-M33 is the first three-stage pipelined Armv8-M based processor and stands as one of the more powerful ARM MCUs [18].

| Extension         | Description                                                                                    |

|-------------------|------------------------------------------------------------------------------------------------|

| RV32I v2.1        | Base integer instruction set with 32-bit registers [5]                                         |

| M v2.0            | Integer multiplication and division instructions [5]                                           |

| A v2.1            | Atomic memory operations [5]                                                                   |

| C v2.0            | Compressed 16-bit instructions for reduced code size [5]                                       |

| Zicsr v2.0        | CSR read/write instructions [5]                                                                |

| Zifencei v2.0     | Instruction-fetch fence for self-modifying code [5]                                            |

| Zba v1.0.0        | Address generation bit manipulation instructions [11]                                          |

| Zbb v1.0.0        | Basic bit manipulation instructions [11]                                                       |

| Zbc v1.0.0        | Carry-less multiplication instructions [11]                                                    |

| Zbs v1.0.0        | Single-bit manipulation instructions [11]                                                      |

| Zbkb v1.0.1       | Bit manipulation for cryptography [12]                                                         |

| Zcb v1.0.3-1      | Code size reduction with additional compressed instructions [13]                               |

| Zcmp v1.0.3-1     | Push/pop and double move compressed instructions [13]                                          |

| Machine ISA v1.12 | Machine-mode privileged instructions [14]                                                      |

| Debug v0.13.2     | External debug support [15]                                                                    |

| Xh3bextm          | Custom bit extraction multiple instructions ( <code>h3.bextm</code> , <code>h3.bextmi</code> ) |

| Xh3irq            | Custom interrupt controller                                                                    |

| Xh3pmpm           | Custom CSRs for M-mode Physical Memory Protection (PMP) enforcement                            |

| Xh3power          | Custom power management with <code>msleep</code> CSR and hint instructions                     |

Table 1: RISC-V extensions supported by Hazard3

The RP2350 supports both Secure and Non-Secure states through the ARM TrustZone technology [3, Chapter 3.7.2]. This thesis focuses on the Non-Secure state of the Cortex-M33, as RIOT does not have a merged integration of this technology [7], and the Hazard3 exclusively supports Non-Secure mode. Thus, the Non-Secure mode is the only common denominator between the two architectures.

Figure 2: Overview of a PIO state machine. Showcasing the shared instruction memory, access to the FIFO buffer, and interrupts.

#### 2.4.4 Programmable Input/Output (PIO)

Programmable Input/Output (PIO) is a distinctive feature of the Raspberry Pi Pico MCU family. It was first introduced in the RP2040 and has been updated in the RP2350 [3, Chapter 11.1.1].

The RP2350 contains three identical PIO blocks. Each block includes four state machines programmable in a custom assembly language. The state machines can operate independently or in parallel, allowing complex I/O operations to be offloaded from the main processors.

In total, the PIO assembly language has nine instructions, as explained in Table 2, that, when combined, allow for fairly complex operations, such as generating precise waveforms, handling serial protocols, or bit-banging custom interfaces. [3, Chapter 11.4].

Each state machine (Figure 2) can read and write to a FIFO buffer, which can be used to communicate with the main processors. In total, each state machine has eight 32-bit buses, by default configured as four inputs and four outputs. This design allows for flexible communication between the state machines and the main processors.

| Instruction | Description                                          |

|-------------|------------------------------------------------------|

| JMP         | Jump to address if condition is true                 |

| WAIT        | Stall until condition is met (GPIO/pin/IRQ/jmppin)   |

| IN          | Shift data from source into Input Shift Register     |

| OUT         | Shift data from Output Shift Register to destination |

| PUSH        | Push ISR contents to RX FIFO                         |

| PULL        | Pull data from TX FIFO into OSR                      |

| MOV         | Move data between registers                          |

| IRQ         | Set or clear IRQ flags                               |

| SET         | Set pins or register to immediate value              |

Table 2: PIO assembly instructions

For high bandwidth operations, the RP2350 supports eight unidirectional 32-bit buses, allowing for eight input or eight output buses exclusively [3, Chapter 11.5.3].

Each state machine can also trigger and respond to interrupts. In total, there are eight IRQ flags shared among all state machines. State machines can both trigger and wait for these IRQ flags [3, Chapter 11.4.11].

In total, each state machine has four registers:

- The X and Y registers are general-purpose registers that can be used for arithmetic and logic operations.

- The Input Shift Register (ISR) and Output Shift Register (OSR) are used for serial data input and output operations.

The instruction memory is shared between all state machines in a block. Holding a total of 32 instructions per block.

PIO runs on the system clock. This would, however, be too fast for most I/O operations. To mitigate this, each state machine has a configurable clock divider that can be used to slow down the execution of instructions.

The clock divider modifies the number of clock cycles that count as one execution cycle of the state machine, instead of reducing the clock frequency [3, Chapter 11.5.5].

#### 2.4.5 Inter-Processor Communication

The RP2350 features a few different mechanisms that enable synchronization and communication between its cores.

#### 2.4.5.1 Spinlocks

The RP2350 includes 32 hardware spinlocks and an additional 32 software locks for Secure mode. Each spinlock is a single flag bit that can be set or cleared by either core. If a core tries to acquire a lock that is already held by the other core, it will spin in a loop until the lock is released [3, Chapter 3.1.4].

#### 2.4.5.2 Atomic Memory Operations

The RP2350 supports atomic access to SRAM based on the Armv8-M Global Exclusive Monitor mechanism. The implementation covers nearly all atomic RISC-V operations as defined in the atomicity PMA specification, except for the Load-Reserved/Store-Conditional (LR/SC) `RsrvEventual` option [3, Chapter 2.1.6].

Load-Reserved/Store-Conditional (LR/SC) is a pair of instructions used in RISC-V to implement read-modify-write operations. The LR instruction loads a value from memory and marks the address as “reserved”. The SC instruction attempts to store a new value to the same address, but only if it is still marked as reserved (i.e., no other writes have occurred to that address since the LR). If the store is successful, it indicates that the operation was atomic; otherwise, it fails, and the operation must be retried [5].

There are three support levels for LR/SC PMA reservability:

- `RsrvNone`: No LR/SC operations are supported (locations are not reservable)

- `RsrvNonEventual`: LR/SC operations are supported, but the reservation may be lost

- `RsrvEventual`: LR/SC operations are supported and guarantee eventual success

The RISC-V Privileged Architecture specification recommends support for `RsrvEventual` and states that `RsrvNonEventual` support should include fallback mechanisms when lack of progress is detected [14, Chapter 3.6.3.2].

Raspberry Pi justifies not supporting `RsrvEventual` by noting that while artificial scenarios without progress guarantees can be theoretically constructed, practical implementations with properly bounded atomic sequences typically complete quickly without requiring additional fallback mechanisms [3, Chapter 2.1.6].

#### 2.4.5.3 Doorbell

The RP2350 features a core-local doorbell interrupt (identified as `SIO_IRQ_BELL` at IRQ 26) that can be triggered by either core or by itself. This mechanism enables event signaling between cores in scenarios where event ordering is not critical or where multiple events can be processed within a single interrupt handler [3, Chapter 3.1.6].

#### **2.4.5.4 Inter-Processor FIFOs**

The primary inter-processor communication mechanism consists of two hardware FIFOs, each 32 bits wide and four elements deep. Each FIFO is readable by one core and writable by the other. The FIFOs support interrupt generation when non-empty (for the reading core) or non-full (for the writing core) [3, Chapter 3.1.5].

These FIFOs are utilized by both the RP2350 bootloader and the multicore startup procedure, as discussed further in Section 5.3

# 3 Related Work

This chapter reviews existing work relevant to the implementation of RIOT OS support for the RP2350. It examines prior efforts in porting operating systems to embedded architectures, security analyzes of the RP2350 platform, and alternative operating systems and frameworks that support the RP2350. These works provide context for the design decisions and implementation approaches taken in this thesis.

## 3.1 Inferno OS on ARMv7-M

A relevant contribution in this field is the masters thesis “Porting Inferno OS to ARMv7-M and Cortex-M7” by Petter Duus Berven [19]. In that work, the author ported the Inferno operating system, a distributed non-real-time OS derived from Plan 9, to the ARMv7-M architecture used in Cortex-M MCUs.

Plan 9 is an operating system developed at Bell Labs in 1992, designed with a focus on distributed computing and simplicity [20]. In Plan 9 only the most core and essential components are part of the kernel<sup>6</sup>, while most other functionality is run outside the kernel<sup>7</sup>. Inferno OS, similar to RIOT OS, allows a fairly modular design, with a small kernel.

The thesis focused on extending the custom compiler toolchain of Inferno to generate ARM Thumb instructions, implementing low-level hardware support for the Teensy 4.1 board, and adapting core kernel components. In his thesis, Berven highlights common challenges including incomplete compiler backends, limited instruction-set coverage, and the need to redesign low-level exception handling, memory layout, and startup code.

While Berven’s project targeted a homogeneous ARM-based environment, this work is relevant to the current thesis as it provides insights into the complexities of porting an

---

<sup>6</sup>Called ‘devices’ in Plan 9 [20].

<sup>7</sup>Called ‘servers’ in Plan 9 [20].

operating system to a different architecture, which can inform the approach taken for porting RIOT OS to the RP2350.

### **3.2 Security through Transparency: Tales from the RP2350 Hacking Challenge**

In “Security through Transparency: Tales from the RP2350 Hacking Challenge” [21], the authors discuss the security aspects of the RP2350 architecture that were found in the process of a hacking challenge organized by Raspberry Pi Ltd. They analyze various vulnerabilities and attack vectors, providing insights into the security challenges associated with heterogeneous architectures. In it, the authors discuss attacks on the One-Time Programmable (OTP) Power State Machine (PSM), vector boot and signature verification to bypass secure boot.

While the main focus of the paper is on exploring the security of the RP2350 and methods to defeat it, the paper provides a comprehensive overview of the underlying hardware and boot sequence of the RP2350, which aids in understanding the low-level initialization of the RP2350 when implementing RIOT OS support.

Although this thesis does not focus on security aspects, as discussed in Section 2.4.3, RIOT OS TrustZone support is out of scope and not yet merged into mainline RIOT OS, understanding the security features of the RP2350 remains important for future work building upon this thesis.

### **3.3 Evaluation of RISC-V Physical Memory Protection in Constrained IoT Devices**

In “Evaluation of RISC-V Physical Memory Protection in Constrained IoT Devices” [17], Bennet Blischke explores the use of the RISC-V Physical Memory Protection (PMP) unit in the context of constrained IoT devices running RIOT OS. In his thesis, Blischke implements data execution prevention and thread stack overflow detection using the RISC-V PMP, evaluating its effectiveness and performance impact.

While this does not directly relate to the RP2350 porting effort, his work serves as a foundation for demonstrating the benefits of enabling RIOT OS support on the RP2350 platform, as it allows leveraging the RISC-V PMP features on the Hazard3 core with minimal additional effort.

One of the conclusion of this work is that most existing PMP implementations do not properly comply with the specifications, we will extend the findings of this work in Section 6 when evaluating the PMP implementation of the Hazard3 core in the RP2350.

### 3.4 ArielOS

In “Ariel OS<sup>8</sup>: An Embedded Rust Operating System for Networked Sensors & Multi-Core Microcontrollers,” the authors present ArielOS a new operating system for embedded devices, written in Rust. It aims to provide a safe and secure environment for IoT applications, including support for multicore MCUs [22]. While still retaining much of the design philosophy of RIOT OS, ArielOS focus on multicore systems differentiates it from RIOT OS.

ArielOS includes support for the RP2350 from the beginning, making it an interesting point of comparison for this thesis. It was designed with the RP2350 and similar systems in mind [22, Chapter 1]. RIOT OS, on the other hand, was designed at a time when single-core 8 bit and 16 bit MCUs were fairly common in the embedded space [4, Section 2], which is something that ArielOS does not target or support.

Under the hood, ArielOS differs significantly from RIOT OS. It leverages the pre-existing Rust ecosystem for embedded systems, using libraries such as Embassy as building blocks for the operating system [22, Chapter 5]. This is in contrast to RIOT OS, which implements most of its functionality from scratch in C.

Embassy is an asynchronous runtime for embedded systems in Rust, providing abstractions for concurrency and hardware access<sup>9</sup>. In the case of the RP2350, ArielOS uses Embassy for the underlying hardware access, binding the implementation offered by the `embassy_rp` crate to its own abstractions<sup>10</sup>.

Referring to Figure 1 as explained in Section 2.3.2, this means that compared to RIOT OS, ArielOS still offers abstraction layers, but the underlying implementation of `cpu`, `drivers`, and `peripherals` is provided by Embassy rather than being originated from the OS<sup>11</sup>. ArielOS then provides core system services such as multicore task scheduling, inter-

---

<sup>8</sup>ArielOS can be found here (Accessed 28.10.2025): <https://github.com/ariel-os/ariel-os>

<sup>9</sup>Embassy can be found here (Accessed 28.10.2025): <https://github.com/embassy-rs/embassy>

<sup>10</sup>`embassy_rp` can be found here (Accessed 30.10.2025): <https://github.com/embassy-rs/embassy/tree/main/embassy-rp>

<sup>11</sup>The implementation of the RP2350 in ArielOS can be found here (Accessed 30.10.2025): <https://github.com/ariel-os/ariel-os/tree/main/src/ariel-os-rp>

Figure 3: ArielOS Scheduler Architecture. After startup, Core 0 initializes the system and starts Core 1 via the FIFO (See Section 2.4.5.4). Then, both cores run the same scheduler, triggered through FIFO messages from either core to handle task scheduling.

process communication, and memory management on top of Embassy, similar to how RIOT OS builds its core services on top of its own hardware abstractions.

The scheduler in ArielOS is designed as a continuation of the tickless real-time scheduler of RIOT OS with preemptive priority scheduling, extended to support multicore systems. The exploration of multicore scheduling is further expanded in the original master’s thesis “Multicore Scheduling and Synchronization on Low-Power Microcontrollers using Embedded Rust” by Elena Frank in which she explores the design and implementation of a multicore scheduler for RIOT-*rs*, which later evolved into ArielOS [23].

ArielOS utilizes a global scheduling approach, as shown in Figure 3, where tasks are not bound to a specific core (though they can have a core affinity if desired), together with a shared mutually-exclusive kernel design [22, Chapter 5D]. The authors argue that such a global scheduling approach is acceptable on IoT MCUs given the low number of cores and limited parallelism [22, Chapter 5B].

On the RP2350, it uses the same process to start both cores as described in Section 5.3. After the startup process, it uses the FIFO to pass scheduler invocations between the two cores [22, Chapter 6B]. Specifically, when the scheduler needs to be invoked in a multicore

system, ArielOS uses a global spinlock through the RP2350 FIFO to synchronize a global critical section for all cores [22, Chapter 5F].

ArielOS represents a different approach to supporting the RP2350 compared to the work done in this thesis as it modifies the concept of the RIOT OS scheduler to support multicore systems directly, rather than building around the existing RIOT OS scheduler design, which is inherently single-core. Nonetheless, given its similarity to the RIOT OS scheduler, ArielOS provides a valuable comparison for the multicore design decisions made in this thesis and how they can be improved in future work. ArielOS also demonstrates that supporting the RP2350 in an embedded operating system is feasible and can provide a solid foundation for further exploration of heterogeneous architectures in embedded systems.

## 3.5 Pico SDK

Pico SDK is the official software development kit for the Raspberry Pi Pico<sup>12</sup>. Compared to RIOT OS or other operating systems, the Pico SDK is designed solely for the Pico series, similar to other vendor SDKs such as esp-idf from Espressif<sup>13</sup>.

The SDK aims to be a development framework rather than a full operating system, providing low-level access to the hardware and basic libraries for common tasks, but not including the benefits that come with a full operating system.

Given that this is a vendor SDK, it offers the widest support for RP2350 hardware features. It uses a CMake build system for building applications. The user must manually specify which modules to include in their application, similar to how RIOT OS allows users to select modules at compile time.

### 3.5.1 Abstraction

One of the core themes of this thesis is the abstraction of architectural differences between the ARM and RISC-V cores in the RP2350. The Pico SDK uses compile-time flags to differentiate between the two architectures.

It also shares a common abstraction layer between the RP2040 and RP2350, mostly sharing headers and higher-level libraries. The RP2040 was the predecessor of the RP2350, sharing most peripherals, though having a different purely ARM Cortex-M0+

---

<sup>12</sup>PicoSDK can be found here (Accessed 28.10.2025): <https://github.com/raspberrypi/pico-sdk>

<sup>13</sup>esp-idf can be found here (Accessed 28.10.2025): <https://github.com/espressif/esp-idf>

dual-core architecture. While not supporting all peripherals, RIOT OS does also offer support for the RP2040.

While this approach works well for a vendor SDK, it lacks the modularity and flexibility of RIOT OS. The Pico SDK approach is hardware-dependent by design, making it less suitable for applications that require portability across different architectures and boards.

Throughout the technical specification and documentation of the RP2350, the Pico SDK is often referenced to explain hardware details, making it an important resource when implementing support for the RP2350 in RIOT OS. This influenced various parts of the implementation described in Section 5.

### 3.6 ZephyrOS

In contrast to the Pico SDK, ZephyrOS is a full-fledged operating system for embedded devices, very similar to RIOT OS<sup>14</sup>. ZephyrOS is maintained by the Linux Foundation and has a large community of contributors.

While RIOT OS is historically largely developed in the context of academic research through volunteer contributions, ZephyrOS is backed by major industry players such as Google, Meta, ARM, Intel, Texas Instruments, Nordic, STMicroelectronics, and others<sup>15</sup>.

This allows ZephyrOS to have vastly larger support for hardware platforms, architectures, and features compared to RIOT OS, supporting 881 boards as of October 2025<sup>16</sup>.

While working on this thesis, ZephyrOS added support for the RP2350, including Hazard3 support, by the end of September 2025<sup>17</sup>. While this did not directly influence the work done in this thesis, it supported decisions made throughout the implementation process, as the approach in ZephyrOS aligned with the approach taken in this thesis regarding the abstraction of architectural differences between the ARM and RISC-V cores and handling the Hazard3 xh3irq interrupt controller (see Section 5.2).

---

<sup>14</sup>ZephyrOS can be found here (Accessed 30.10.2025): <https://github.com/zephyrproject-rtos/zephyr>

<sup>15</sup>ZephyrOS project members (Accessed 28.10.2025): <https://www.zephyrproject.org/project-members/>

<sup>16</sup>ZephyrOS supported boards (Accessed 30.10.2025): <https://docs.zephyrproject.org/latest/boards/index.html>

<sup>17</sup>ZephyrOS RP2350 Hazard support PR (Accessed 30.10.2025): <https://github.com/zephyrproject-rtos/zephyr/pull/89758>

# 4 Analysis and Design

In this chapter we analyze potential design considerations and requirements for porting RIOT OS to the RP2350 MCU.

This includes the bootup sequence, interrupt controller, clock system, and threading model. This gives us a good framework to then implement the necessary low-level support and ensure that RIOT OS can effectively utilize the capabilities of the RP2350.

## 4.1 Bootup Sequence

### 4.1.1 Bootrom

The RP2350 features a built-in bootrom that is executed on power-up [3, Chapter 5.2.2]. This bootrom is stored directly at `0x0` in a 32 kB immutable memory region and flashed onto the device during manufacturing [3, Chapter 4.1].

The bootrom has a wide range of responsibilities, from boot slot selection to rollback protection, intended for secure applications [3, Chapter 5]. However, for the context of this thesis, the most relevant parts of the bootrom are:

- Image and partition definition using picobin blocks

- Bootloader

- Architecture switching

- Core 0 boot code

- Core 1 launch preparations

### 4.1.2 Flashing

This thesis focuses on two primary flashing methods for the RP2350: OpenOCD and Picotool. These cover the most common use cases for flashing RIOT OS onto the RP2350, either through a SWD debugger or through USB mass storage device mode, thus offering flexibility for different development setups.

The RIOT build system abstracts the flashing process through the `PROGRAMMER` variable, allowing users to select their preferred flashing method through the build system, making it easy to switch between different flashing methods without dealing with the underlying implementation details.

An MCU must simply declare their supported programmers, and offer relevant config options, such as the OpenOCD target file.

### 4.1.2.1 OpenOCD / Debugprobe

OpenOCD (Open On-Chip Debugger) is a popular open-source tool for debugging and programming embedded devices using JTAG/SWD interfaces, including acting as a remote target for GDB<sup>18</sup>.

The RP2350 allows for flashing and debugging through a SWD interface. Raspberry Pi recommends using their Debugprobe<sup>19</sup> or a secondary Raspberry Pi Pico 1/2 as a SWD debugger flashed with a debugprobe firmware<sup>20</sup> [24, Appendix A].

OpenOCD support for the RP2350 is, as of October 2025, still not integrated into any mainline OpenOCD release, requiring a custom build with RP2350 support<sup>21</sup>. RIOT OS already has support for OpenOCD as a flashing method, thus, as long as the custom OpenOCD build is used, no additional changes are required to support OpenOCD flashing for the RP2350.

### 4.1.2.2 Picotool

`picotool` is a custom command-line tool developed by Raspberry Pi for interacting with Raspberry Pi Pico series over USB<sup>22</sup>. RIOT already had support for `elf2uf2`, a predecessor to `picotool`, used for converting ELF files to the UF2 format used by the RP2040. `Picotool` support is thus a natural extension of this existing functionality and can reuse a significant portion of the existing integration codebase within RIOT OS.

UF2 (USB Flashing Format) is a file format developed by Microsoft designed for flashing MCUs over USB mass storage device mode. It allows users to simply drag and drop firmware files onto the device when it appears as a USB drive<sup>23</sup>.

---

<sup>18</sup>OpenOCD official website (Accessed 03.11.2025): <http://openocd.org/>

<sup>19</sup>Debugprobe product link (Accessed 30.10.2025): <https://www.raspberrypi.com/products/debugprobe/>

<sup>20</sup>The debugprobe firmware can be downloaded here (Accessed 28.10.2025): <https://github.com/raspberrypi/debugprobe>

<sup>21</sup>The RP2350 OpenOCD fork can be found here (Accessed 23.10.2025): <https://github.com/raspberrypi/openocd>

<sup>22</sup>Picotool official repository (Accessed 30.10.2025): <https://github.com/raspberrypi/picotool>

<sup>23</sup>UF2 repository (Accessed 28.10.2025): <https://github.com/microsoft/uf2>

Upon selecting `picotool` as the **PROGRAMMER**, the RIOT build system will automatically clone and build `picotool`. It then converts the compiled binary into the UF2 format, verifies that the UF2 file is valid, and finally uses `picotool` to flash the UF2 file onto the RP2350 over USB.

#### 4.1.3 Image and Partition Definition (Picobin)

##### 4.1.3.1 Background

For the bootrom to load an application from flash, it needs to understand the specifics of the image in question, given the heterogeneous nature of the RP2350. To allow such specifications the bootrom uses picobin blocks [3, Chapter 5.1.4].

The block described in Table 3 should be placed within the first 4kB of flash memory. The bootrom will parse this block to determine which image to load based on the current architecture and security state of the core [3, Chapter 5.1.5.1].

A single binary can have multiple picobin blocks to support different architectures and security states. The **Next Block Pointer** field indicates the relative position.

| Field              | Description                                                                                                                                                                                                                                                                                                                                                    |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Block Start Marker | Marks the beginning of a picobin block (Magic Value)                                                                                                                                                                                                                                                                                                           |

| Item Type          | Type of items in the block (e.g. Image Definition)                                                                                                                                                                                                                                                                                                             |

| Item Size          | Block size in words                                                                                                                                                                                                                                                                                                                                            |

| Image Type Flags   | <ul style="list-style-type: none"> <li>Bit 0-3: Image Type (e.g. Executable, Data)</li> <li>Bit 4-5: Security (e.g. Secure, Non-Secure)</li> <li>Bit 6-7: Reserved</li> <li>Bit 8-10: CPU Architecture (e.g. RISC-V, ARM)</li> <li>Bit 11: Reserved</li> <li>Bit 12-14: Chip (e.g. RP2350, RP2040)</li> <li>Bit 15: Try Before You Buy (TBYB) Image</li> </ul> |

| Last Item Marker   | Marks the last item in the block                                                                                                                                                                                                                                                                                                                               |

| Last Item Size     | Size of last item in words                                                                                                                                                                                                                                                                                                                                     |

| Next Block Pointer | Relative pointer to next block (0 = self = no more blocks)                                                                                                                                                                                                                                                                                                     |

| Block End Marker   | Marks the end of the picobin block (Magic Value)                                                                                                                                                                                                                                                                                                               |

Table 3: Picobin block structure for RP2350 image definition

#### 4.1.3.2 Design Considerations

Incorporating a picobin block into the RIOT OS build process involves a few key design considerations. First, the build system must be able to generate the picobin block with the correct fields based on the target architecture and security settings. This includes setting the appropriate `Image Type Flags` to indicate whether the image is for ARM or RISC-V and then link that binary blob into the final firmware image.

To achieve this, we must first look into how RIOT OS handles the build process and most notably how it manages linker scripts for different architectures.

The CPU defines a custom linker script under the `ldscripts` directory. In the case of the ARM version of the RP2350, this file would be `ldscripts/rp2350_arm.ld`. However, since both the ARM and RISC-V versions use an even higher abstraction layer through the `cortexm_common` and `riscv_common` module respectively, the actually important linker script is provided by these common modules, thus `ldscripts/rp2350_arm.ld` simply uses the `INCLUDE` directive to include the relevant common linker script.

This, however, poses a challenge as the aforementioned common linker scripts do not provide any hooks for adding custom sections, such as the picobin block. As such, there are two different approaches to solve this problem:

- Modify the common linker scripts to include hooks for custom sections.

- Create a new linker script specifically for the RP2350 that includes the picobin block.

Since these common modules are used by multiple MCUs, modifying them could potentially introduce issues for other platforms. In the case of the `cortexm_common` module, the linker script is fairly lengthy and complex.

## 4.2 Interrupt Controller

Interrupt handling on the RP2350 is complex due to the heterogeneous design. Each architecture has its own interrupt controller, with the ARM cores using a NVIC and the Hazard3 cores using the XH3IRQ controller [3, Chapter 3.8.4.2].

To facilitate cross-architecture compatibility, the RP2350 keeps the identical Interrupt Requests (IRQs) numbers for both, including support for platform-specific interrupts on both architectures [3, Chapter 3.2].

The RISC-V Machine-mode timer interrupt `SI0_IRQ_MTIMECMP`, for instance, is a standard privileged interrupt for RISC-V RV32I. However, both on the Hazard3 and Cortex-M33, the IRQ is mapped to the value 29 and is functional [3, Chapter 3.1.8].

In total, the RP2350 defines 52 IRQ signals. The first 46 IRQ signals are connected to peripheral interrupt sources, while the remaining 6 are intentionally hardwired to 0 for forceful self-interrupts via software [3, Chapter 3.2].

#### 4.2.1 Nested Vectored Interrupt Controller (NVIC)

NVIC is a nested vectored interrupt controller designed by ARM for their Cortex-M series of processors. It provides a flexible and efficient way to manage interrupts, allowing for prioritization and preemption of ISRs. It also handles context saving and restoring during interrupt handling. The NVIC design uses a vector table to map IRQ numbers to their corresponding ISR addresses, in which the first entries are reserved for system exceptions, followed by device specific interrupts [25].

On the Cortex-M33, the NVIC allows up to 480 interrupts to be managed with a preemption level of 0 to 255, whereby a lower level signals a higher priority [26]. As opposed to the custom XH3IRQ controller on the Hazard3 core, the NVIC on the RP2350 Cortex-M33 follows the standard ARM design without any modifications.

#### 4.2.2 XH3IRQ Controller

To minimize architectural differences, the Hazard3 core includes an interrupt controller extension called XH3IRQ. This extension adds a new set of Control and Status Registers (CSRs) and instructions to the core that enable an interrupt handling mechanism similar to ARM NVIC.

To facilitate this, the XH3IRQ controller adds 6 custom CSRs, as described in Table 4.

| CSR                     | Description                                                                                |

|-------------------------|--------------------------------------------------------------------------------------------|

| <code>meiea</code>      | Machine External Interrupt Enable Array (enables/disables interrupts)                      |

| <code>meipa</code>      | Machine External Interrupt Pending Array (status of interrupts)                            |

| <code>meifa</code>      | Machine External Interrupt Force Array (force interrupts)                                  |

| <code>meipra</code>     | Machine External Interrupt Priority Array (priority levels for interrupts)                 |

| <code>meinext</code>    | Machine External Interrupt Next (pointer to next highest priority pending interrupt)       |

| <code>meicontext</code> | Machine External Interrupt Context (Saves/informs about context during interrupt handling) |

Table 4: XH3IRQ custom CSRs for interrupt management [1, Chapter 4.1]

The XH3IRQ controller handles enabling, status, priority, and forced pending through a window system, as shown in Table 5.

| Bits  | Name   | Description                                                                                                          |

|-------|--------|----------------------------------------------------------------------------------------------------------------------|

| 31:16 | window | 16-bit read/write window into the external interrupt array (1 bit per interrupt)                                     |

| 15:5  | -      | Reserved                                                                                                             |

| 4:0   | index  | Write-only, self-clearing field (no value is stored) used to control which window of the array appears in the window |

Table 5: XH3IRQ CSRs register fields for Interrupt Pending Array (`meipa`), Interrupt Enable Array (`meiea`), Force Interrupt Array (`meifa`)

This window system, described in Table 5 allows the XH3IRQ controller to manage 512 interrupts while only using a 32-bit CSR. Thus, at 1 bit per interrupt, each window can manage 16 interrupts with 32 total windows [1, Chapter 3.8.1].

| Bits  | Name   | Description                                                                                                      |

|-------|--------|------------------------------------------------------------------------------------------------------------------|

| 31:16 | window | 16-bit read/write window into the external interrupt array (4 bits per interrupt)                                |

| 15:5  | -      | Reserved                                                                                                         |

| 6:0   | index  | Write-only, self-clearing field (no value is stored) used to control which window of the array appears in window |

Table 6: XH3IRQ CSRs register fields for the Interrupt Priority Array (`meipra`)

To allow 16 preemption levels, the interrupt priority array CSR uses a 7-bit index instead with a 4-bit value per interrupt, as described in Table 6. Thus, each window can manage 4 interrupts with a total of 128 windows [1, Chapter 3.8.4].

The XH3IRQ controller supports two operational modes: direct and vectored. In direct mode, the interrupt handler address is fixed, and all interrupts jump to the same handler. In vectored mode, each interrupt can have its own handler address [1, Chapter 4.1].

The XH3IRQ controller also includes a context-saving mechanism that allows the current execution context to be saved and restored when handling interrupts. This is done using the `meicontext` CSR and can optionally be enabled [1, Chapter 3.8.6].

Once the context is saved, the interrupt handler can be executed. After the handler is finished, the context can be restored and execution can continue from where it was interrupted through a `mret` call after completing the ISR [1, Chapter 3.2.9].

This is similar to the way ARM NVIC handles context saving and restoring during interrupt handling, as both controllers automatically save the execution context when an interrupt occurs, allowing the processor to jump to the interrupt handler. After the handler completes, the original context gets restored, and execution resumes from the point of interruption. Additionally, both support preemption priorities, for which higher-priority interrupts can interrupt lower-priority ones, ensuring critical tasks are handled promptly.

### 4.2.3 Design Considerations

When designing the interrupt handling for the RP2350 port in RIOT OS, the goal is to create a unified abstraction layer that could handle interrupts for both architectures seamlessly. At the same time though, conforming to existing interrupt handling mechanisms of RIOT for both architectures. Specifically, this means that we first needed to understand the existing interrupt handling mechanisms for both architectures in RIOT OS.

#### 4.2.3.1 Cortex-M Interrupt Handling

The `cortexm_common` module in RIOT already includes support for the NVIC, thus the design considerations for the RP2350 port were mostly about ensuring that the implementation we intend to provide for the Hazard3 XH3IRQ controller conforms to the existing design patterns used in the `cortexm_common` module, at least in a way that allows architecture-agnostic code to work seamlessly across both architectures.

In RIOT the NVIC implementation uses a macro-based approach, in which the `cpu` module provides an extension to the interrupt vector table. Each vector that should be included in the final vector table gets a `.vector` label assigned using the `__attribute__((used,section(".vectors." # x)))` attribute. These attributes are then collected at the linking stage using a `KEEP(*(SORT(.vectors*)))` and sorted based on the assigned `x` value.